- CMOS 이미징 기술의 발전

CMOS 이미징 기술에서의 설계 및 제조에 대한 개선 및 혁신으로 전통적이고 실용적인 구현 문제를 많이 극복할 수 있습니다. 집적 회로 설계는 항상 한계 사이의 최적화 트레이드오프의 과정이지만, CMOS이미징 기술 디자이너들은 이제 머신 비전 애플리케이션을 위한 진정 경쟁력있는 성능으로 제품을 제공할 수 있습니다. 이러한 혁신 및 상당한 시간 및 투자로, CMOS 이미징 기술은 상당한 발전을 보여줬고 머신 비전 산업의 장비 업체들에 의해CCD 기술과 경쟁하여 사용률이 증가하고 있습니다.

특정 머신 비전 애플리케이션에 가장 적합한 카메라를 선택할 때 머신 비전 시스템을 필요로 하는 이미지 센서 및 카메라의 다양한 속성들에 대한 정교한 균형이 필요합니다. 지난 10년 동안 CMOS기술이 만들어낸 과정은 고속 검사를 위한 기술이었습니다.

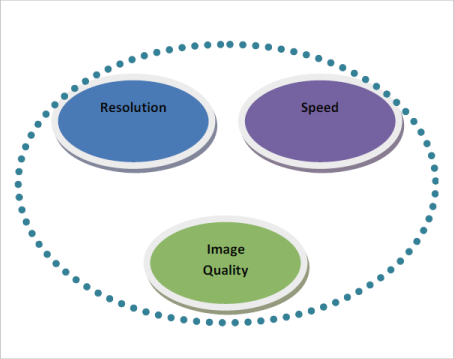

3개의 주요 특성은 area scan 이미징 장치에 대한 트레이드 오프 기본 세트를 정의합니다. 첫 번째 속성 세트는 이미징 성능을 볼 수 있습니다. 이미지 품질, 초당 최대 프레임 수, 해상도 두 번째 속성 세트는 어려운 결정을 요구하는 경쟁 기능인 카메라 또는 센서의 기능에서의 트레이드 오프 속성입니다. 이러한 두 번째 트레이드 오프 속성의 예는 windowing 및 소모 전력과 같은 기능을 포함합니다. 마지막 속성은 가격, 수율, 안정성, 기타 기능 등을 다루어야 하는 타당성 트레이드 오프로 이미징 장치의 제조와 관련있습니다.

그림 1 : CMOS 이미지 센서 기본 트레이드 오프

과거 많은 애플리케이션에서 이미지 품질 임계값은 ILT CCD 센서(inter-line transfer CCD)를 요구했지만, CMOS 센서의 설계 향상으로 더 나은 이미지 품질을 이끌어냈고 원하는 이미지 품질로 훨씬 빠른 검사 시스템을 위한 새로운 가능성을 열었습니다. 역사적으로, CCD ILT 기술은 shuttered 이미징을 위한 지배적인 센서 기술이었습니다. 첫 번째 세대의 CMOS 기술은 높은 속도, 낮은 전력 및 비용의 기회임에도 불구하고 대부분의shuttered 애플리케이션에서 이것의 사용을 배제하는 롤링 셔터(rolling shutter) 기능만으로 시장에 제공되었습니다. 나중에 CMOS global shutter 기능이 도입되었고 롤링 셔터(rolling shutter)의 부족분을 해결하고 CMOS가 더 많은 사용자들과 관련있도록 하였습니다. 최근 CMOS 기술의 발전은 급격하게 노이즈를 감소하였고SNR(signal to noise ratio) 수준을 향상하였습니다. CMOS 기술은 주요 성능 장애의 마지막이었던 CCD ILT에서 할 수 있었던 것들을 능가합니다. 고속 머신 비전 애플리케이션에서의 CMOS는 CCD ILT 기술의 기능, 성능, 가격 등의 요구를 충족하거나 이를 초과합니다.

최신 CMOS 이미징 기술은 매우 높은 데이터 처리량(throughput), 정말 빠르고 높은 대역폭의 아날로그 - 디지털 컨버터 등을 사용하여 해상도 및 속도 간의 트레이드 오프를 감소하였습니다. 이러한 장치의 속도는CameraLink와 같은 사용할 수 있는 데이터 전송 표준의 경계에 도전하고 있고, 새로운 고대역폭의 CameraLink HS 표준으로 이끄는 추진력이 되었습니다.

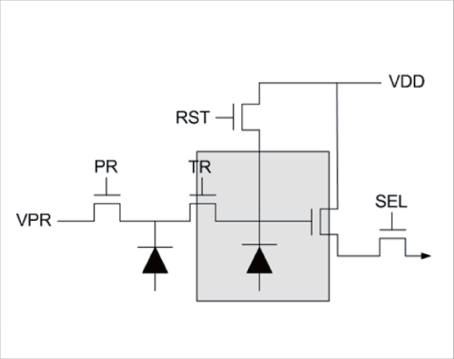

global shutter 픽셀과 같은 픽셀 구조의 발전은 이미 과거의 고속 애플리케이션의 문제였던 속도 및 이미지 품질 사이의 격차를 줄여주었습니다. 이 기술은 현재 모든 고급 CMOS 이미지 센서를 위한 사실상의 표준입니다.

그림 2 : 1999년에 도입된 Teledyne DALSA 5T Global Shutter CMOS Pixel

그림 3 : Global shutter, rolling shutter 및 이미지 왜곡

PPD(Pinned Photodiode Technology) 및 최적화된 임플랜테이션(implantation) 기술과 같은 기능의 사용으로 이미지의 노이즈 및 지연 뿐만 아니라 "핫 픽셀"의 수 및 암전류(dark current)를 줄여줍니다. 이것으로 픽셀 신호를 향상하여 노이즈 비율을 줄일 수 있습니다. 낮은 노이즈 층은 새로운 카메라가 더 적은 빛으로 더 빠른 프레임 레이트를 사용하여도 동일한 이미지 SNR을 달성할 수 있다는 것을 의미합니다.

새로운 CMOS 이미징 기술의 혜택은 CMOS 이미지 센서에 국한되지 않습니다. CMOS 카메라 설계 기술의 진보는 또한 이미징 성능 측면에서 새로운 가능성을 제공하였습니다. 예를 들어, PRNU(pixel response non-uniformity) 보정과 같은 카메라 보정을 실시간 임베디드 프로세싱으로 할 수 있습니다. 카메라에서의 임베디드 프로세싱은 또한 전통적으로 프레임 그래버에서 처리되었던 프로세싱을 수행하여 비전 시스템을 단순화합니다. (예: 카메라 내에서의 실시간 FFC(flat field correction)) Windowing 기능 및 카메라 화면 비율을 변경할 수 있는 능력은 카메라를 설계하는 방법의 다른 예이고 CMOS 이미지 센서와 연계하여 최종 사용자에게 추가 기능을 제공할 수 있습니다.

CMOS 센서 기술 혁명에서의 경쟁 요인

CMOS 픽셀 구조와 관련한 CMOS 이미징 센서의 성능을 정의하는 몇 가지의 근본적인 경쟁 요소가 있습니다. 이러한 트레이드 오프 중 일부는 근본적이고 물리학적인 트레이드 오프이지만, 일부는 장치의 실리콘이나 임플리먼테이션에서의 비완벽성입니다. 과거 CMOS 기술의 주요 초첨 중 하나는 이미지 아티팩트image artifact)를 극복하는 것이었습니다. 사용자는 극단적인 상황 또는 특정 작업 및 조명 조건에서 발생하는 이미지 아트팩트와 관련된 CMOS 이미지 센서의 성능에 세심한 주의를 기울여야 합니다. 설계 트레이드 오프에 직면하였을 때 이러한 고려 사항은 설계자의 결정에 크게 영향을 미칩니다. 이미지 아트팩트image artifact)를 보이는 경우 우수한 사양 조합을 가지고 있는 센서라도 사용할 수 없게 될 것이라는 것을 증명할 수 있습니다.

일부 주요 트레이드 오프 파라미터를 아래에 설명합니다.

A) 필 팩터(Fill Factor)

주어진 픽셀 및 필 팩터(fill factor) 사이의 트랜지스터 개수는 반비례 관계가 있습니다. 필 팩터(Fill factor)는 픽셀에서의 감광대(light sensitive area) 비율로 센서의 감도 및 캡처 이미지의 S/N에 직접 영향을 미칩니다. 반면에, 픽셀이 더 많은 트랜지스터를 가지면 이미지 품질을 향상시킬 수 있는 글로벌 셔터(global shutter) 및CDS(correlated double sampling) 등과 같은 추가 기능을 사용할 수 있습니다.

B) 수광각(Fill Factor)

픽셀 당 증가된 트랜지스터의 수의 영향을 최소하기 위해 대부분의 CMOS 이미지 센서는 마이크로 렌즈를 사용합니다. 마이크로 렌즈는 트랜지스터 수의 증가로 인해 픽셀에서 손실되는 일부를 보정합니다. 그러나, 마이크로 렌즈는 픽셀에서 “수광각(light acceptance angle)”을 줄일 수 있습니다. 마이크로 렌즈를 사용하면 픽셀에서의 트랜지스터 수 및 이미지 품질 사이의 트레이드 오프를 다소 향상시킵니다.

C) PCC(Pixel Charge Capacity) (Qsat) 및 최대 노출 수준

픽셀이 더 많은 트랜지스터를 가지는 데에 대한 또하나의 주요 단점으로는 줄어드는 PCC(pixel charge capacity)입니다. 또한, 픽셀 크기 감소(같은 크기의 센서에서 향상된 해상도)는 더 적은 공간의 전하 스토리지를 의미하고 이 결과로 낮은 PPC(pixel charge capacity)를 의미할까요? 감소된 PCC(pixel capacity)는 일부 애플리케이션에 대한 센서의 적합성에 직접 영향을 미칩니다. 예를 들어, 많은 애플리케이션에서는 카메라가 밝은 이미지에서 회식 음영을 구분해야 합니다. 이러한 애플리케이션에서 샷 노이즈(shot noise)는 결정적인 요소이지만 절대적인 노이즈 플로어(noise floor)가 아닙니다. 캡처한 광자 신호의 사격형 루트로 제한된 범위의 SN비율 때문에 샷 노이즈(shot noise) 제한 애플리케이션은 높은 픽셀 스토리지 용량을 필요로 합니다.

높은 픽셀 저장 용량은 또한 블루밍(blooming) 및 기생 이미지 아티팩트(parasitic image artifact)와 같은 카메라의 비이상적인 여러 유형의 크기를 최소화하는 데 도움이 되고 영향을 미칩니다.

D) 최소 노출 시간(Exposure Time), 해상도, 전원

최소 노출 시간은 카메라의 실질적인 최대 속도를 직접적으로 정의합니다. 최적으로 설계되지 않은 센서는 긴 노출 시간에서는 정상적으로 동작하면서 낮은 노출 시간에서는 이미지 아티팩트image artifact)를 나타낼 수 있습니다. CMOS 센서 설계에서 최소 노출 시간은 센서 내의 신호 전파 속도(signal propagation speed)에 의해 결정됩니다. 전압 안정화는 차선의 신호 라우팅 방식에 의해 손상될 수 있습니다. 이 문제는 센서의 해상도가 증가하면 더욱 분명하게 됩니다. 반면에, 정말 짧은 노출 시간 동안 캡처하기에 충분한 센서의 기록 능력은 또한 아티팩트를 통해 광범위한 노출 제어 피드로 이어질 뿐만 아니라 소비 전력이 높아집니다.

E) 최소 도달 노이즈 수준

픽셀의 최소 도달 노이즈 수준은 적인 빛을 사용해야만 하는 애플리케이션에서 중요합니다. 복잡한 픽셀 회로 및 스테이지 수의 증가는 센서의 노이즈 플로어noise floor)에 부정적인 영향을 미칠 수 있습니다. 이러한CDS(correlated double sampling)과 같은 필수 기술은 픽셀 아키텍처에서 여분의 메모리가 필요합니다. CDS 기능은 CCD ILT 장치와 동등하거나 그 이상의 노이즈 수치를 달성하기 위해 있어야만 합니다. 집광을 위해 이 추가 회로는 픽셀의 적은 영역을 떠나 신호가 저장되므로 광학 효율 및 최대 신호 처리 능력을 제한합니다.

CMOS 글로벌 셔터(global shutter) 픽셀에서 CDS를 구현하는 최적의 방법에 대한 학설들이 존재합니다. 일반적으로 "전하 도메인(Charge Domain)” 기술은 “전압 도메인(Voltage Domain)” 기술보다 뛰어난 점이 많지만 전자(former)가 셔터 누설(shutter leakage)에 더 영향을 받기 쉽습니다.

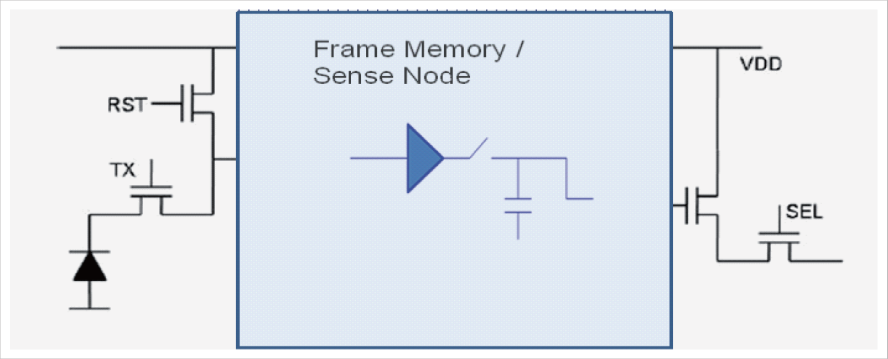

F) 셔터 누설

CMOS 픽셀이 판독되면 픽셀의 감광 영역의 전하는 후속 전하를 위해 스토리지 영역으로 전송된 다음, 전압으로 변환되고 데이터로 전송됩니다. 스토리지 영역이 완벽하게 픽셀의 이미징 영역에 고립되지 않을 수 있기 때문에 스토리지 노드에서 원하지 않는 신호가 수집되어 기생 이미지 아티팩트(image artifact)를 생성할 수 있습니다. 이 전하 누설을 감소하기 위해 전하를 즉시 전압으로 변환하고 샘플링될 수 있습니다. “전압 도메인(voltage domain)” 글로번 셔터(global shutter)로 알려진 이 기술은 별도의 콘덴서를 사용해야 합니다. 하지만, 이 기술의 불리한 면으로는 전하 도메인 CDS와 상대적으로 노이즈 플로어 수준(noise floor level)이 증가될 뿐만 아니라, 이전 부분에서 언급한 성능 파라미터들에 부정적인 영향을 미칩니다.

“전압 도메인(voltage domain)” 글로벌 셔터(global shutter) 구조의 대체 접근 방식으로는 “전하 도메인(Charge Domain)”이라는 차폐된 공간에서 이미지의 전송이 일어나는 “전하 도메인(Charge Domain)” 구조가 있습니다. 이렇게 하면, 픽셀의 복잡도를 크게 줄일 수는 있지만, 픽셀 내에서 구성 요소의 최적화된 구현이 필요합니다. 글로벌 셔터(global shutter) 및 다른 성능 파라미터 사이의 더 좋은 트레이드 오프 방식을 달성하려면CMOS 제조 공정의 어려움을 충족해야만 하고 극복되어야만 합니다. 기본적으로, 이 방법으로 픽셀에서 높은 품질의 요소 개수를 감소하여 더 복잡한 픽셀 회로와 동일한 결과를 얻을 수 있습니다.

그림 4 : 전압 도메인 글로벌 셔터(Voltage Domain Global Shutter) 아키텍처

결론

CMOS 이미징 장치 설계 과정에는 여러 개의 경쟁 요인이 있습니다. 트레이드 오프 중 일부는 기본적이고 장치 동작의 물리학적인 측면과 관련이 있지만 일부는 설계 구현 중에 나타나는 비이상적인 요소들입니다. 좋은 CMOS 이미징 장치를 설계는 최적의 설계를 찾아낼 수 있도록 이러한 요소를 모두 고려해야 합니다.

차세대의 CMOS 기술은 확실히 이미징 장치의 성능을 향상시킬 것입니다. 이제 사용자는 애플리케이션 요구 사항을 초과하는 이미지 품질을 제공하는 고해상도 및 고속 이미징 장치의 혜택을 누릴 수 있습니다. 차세대의 CMOS 기술은 이미징 장치 속성의 유례없는 조합으로 오늘날의 제한 사항을 무시할 것입니다.

유튜브와 블로그에서 더 많은 자료를 보실 수 있습니다.

배너를 클릭하면 해당 페이지로 이동합니다.